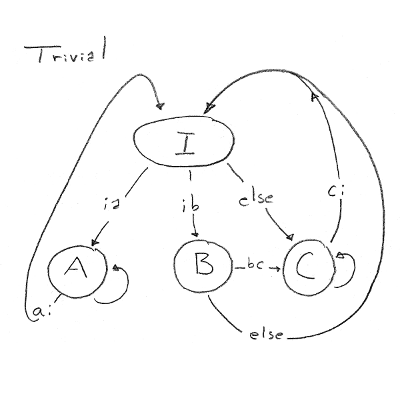

Consider the trivial state machine described and pictured to the right. The Verilog RTL produced by FSMgen.pl (below the bubble diagram) has STATE as a primary output. The path information produced by FSMgen.pl is as follows (from trivial_paths.txt):

BITS=2 CLK=clk RESET=reset STATE :: I : 00 STATE :: A : 01 STATE :: B : 10 STATE :: C : 11 path1:I(ia)A(ai)I path2:I(ib)B(ELSE)I path3:I(ELSE)C(ci)I path4:I(ia)A+(ai)I path5:I(ib)B(bc)C(ci)I path6:I(ELSE)C+(ci)I path7:I(ib)B(bc)C+(ci)I

Using trivial_paths.txt as an input, the script Pathmaker.pl produces one acceptor automata per path. Here is the acceptor automata for path7:

//Path path7 is I(ib)B(bc)C+(ci)I

module path7 (

input [1:0]STATE,

input clk,

input reset,

output [4:0]EXPECTING,

output ok2spin,

output doing,

output done) ;

logic [3:0] FSM ;

logic [3:0] nextstate ;

logic doing ;

logic done ;

localparam I = 2'b00 ;

localparam A = 2'b01 ;

localparam B = 2'b10 ;

localparam C = 2'b11 ;

localparam my_ZERO = 4'd0 ;

localparam my_I = 4'd1 ;

localparam my_B = 4'd2 ;

localparam my_C = 4'd4 ;

localparam my_DONE = 4'd8 ;

assign doing = |FSM ;

assign done = FSM[3] ;

always_comb

begin

if (STATE == I) EXPECTING = B ;

else if (STATE == B) EXPECTING = C ;

else if (STATE == C) EXPECTING = I ;

end

// Registered part of the FSM:

always @(posedge clk or posedge reset)

begin

if (reset) FSM <= my_ZERO ;

else FSM <= nextstate ;

end

// Combinatorial part of the FSM:

always_comb

begin

nextstate = 'bx ;

case (FSM)

my_ZERO : if (STATE == I) nextstate = my_I ;

else nextstate = my_ZERO ;

my_I : if (STATE == B) nextstate = my_B ;

else if (STATE == I) nextstate = my_I ;

else nextstate = my_ZERO ;

my_B : if (STATE == C) nextstate = my_C ;

else nextstate = my_ZERO ;

my_C : if (STATE == I) nextstate = my_DONE ;

else nextstate = my_C ;

my_DONE : nextstate = my_DONE ;

endcase

end

//And a final output

assign ok2spin = (FSM == C) ;

endmodule

trivial.fsm NAME=trivial CLK = clk RESET = reset ENCODING = BINARY INITIALSTATE = I IDLESTATE = I I(ia)A I(ib)B I(ELSE)C A(ai)I B(bc)C B(ELSE)I C(ci)I bored <= I busy1 <= A busy2 <= C

module trivial (

input clk,

input reset,

input ia,

input ib,

input ai,

input bc,

input ci,

output bored,

output busy2,

output busy1,

output [1:0] STATE) ;

localparam I = 2'b00 ;

localparam A = 2'b01 ;

localparam B = 2'b10 ;

localparam C = 2'b11 ;

// State driven outputs:

assign bored = (STATE == I) ;

assign busy2 = (STATE == C) ;

assign busy1 = (STATE == A) ;

// Register part of the FSM

logic [1:0] STATE, nextstate ;

always @(posedge clk or posedge reset)

begin

if ( reset ) STATE <= I ;

else STATE <= nextstate ;

end

// Combinatorial part of the FSM:

always_comb

begin

nextstate = 'bx ;

case (STATE)

I : if (ia) nextstate = A ;

else if (ib) nextstate = B ;

else nextstate = C ;

A : if (ai) nextstate = I ;

else nextstate = A ;

B : if (bc) nextstate = C ;

else nextstate = I ;

C : if (ci) nextstate = I ;

else nextstate = C ;

endcase

end

endmodule